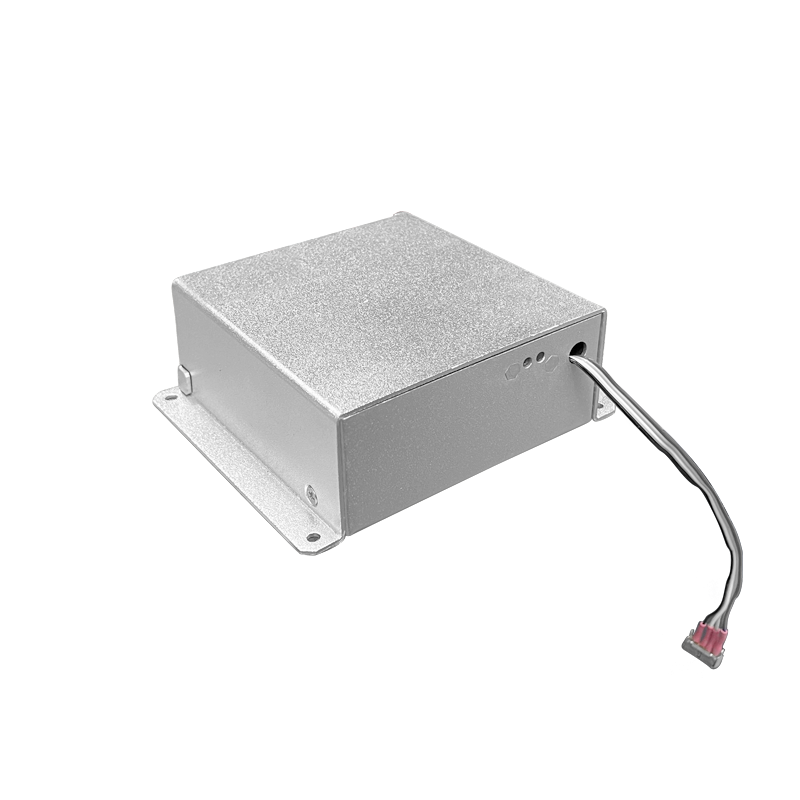

高壓電源在靜電卡盤多通道同步中的關(guān)鍵技術(shù)應(yīng)用

一、靜電卡盤高壓電源的核心作用

靜電卡盤(Electrostatic Chuck, ESC)是半導(dǎo)體制造、精密加工中的核心夾持設(shè)備,其依賴高壓電源(通常為直流,輸出電壓達(dá)數(shù)千伏)在電介質(zhì)表面生成可控靜電場(chǎng),實(shí)現(xiàn)晶片的無(wú)接觸吸附與釋放。傳統(tǒng)單通道電源在應(yīng)對(duì)多晶片并行處理時(shí)面臨兩大挑戰(zhàn):

• 同步性不足:多通道電源若未嚴(yán)格同步,晶片吸附/釋放的時(shí)序偏差會(huì)導(dǎo)致工藝一致性下降,增加破片風(fēng)險(xiǎn);

• 動(dòng)態(tài)響應(yīng)滯后:靜電力的毫秒級(jí)調(diào)控需電源具備高帶寬特性,否則影響溫度均勻性和蝕刻精度。

二、多通道同步的核心技術(shù)方案

為滿足多晶片協(xié)同加工需求,高壓電源的多通道同步技術(shù)需在硬件架構(gòu)和軟件控制上實(shí)現(xiàn)突破:

1. 硬件級(jí)同步機(jī)制

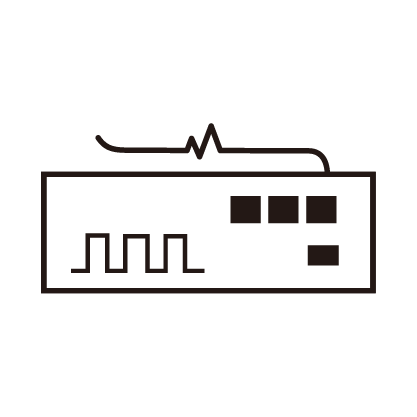

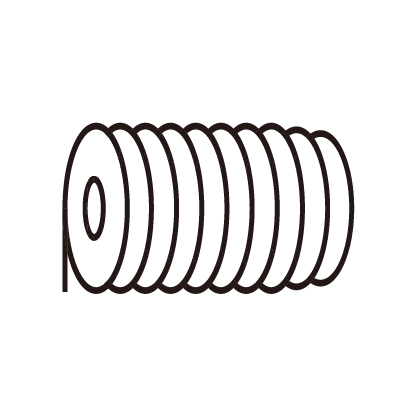

• 時(shí)鐘信號(hào)分配:采用高穩(wěn)定性晶振(如TCXO)生成主時(shí)鐘,通過(guò)同步隔離變壓器或高速串行鏈路(如JESD204B協(xié)議)分發(fā)至各通道,確保時(shí)序偏差≤10ns。

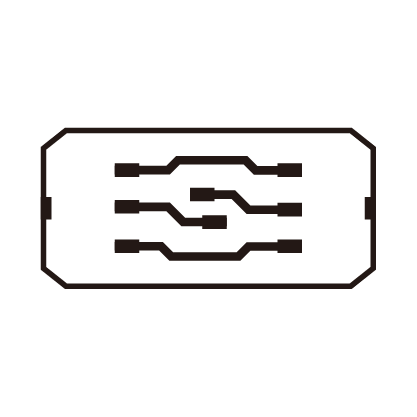

• 相位鎖定技術(shù):每個(gè)電源通道集成PLL(鎖相環(huán)),實(shí)時(shí)校準(zhǔn)本地時(shí)鐘與主時(shí)鐘相位,抑制溫度漂移和噪聲干擾。

2. 軟件協(xié)同控制

• 確定性延遲模型:基于協(xié)議(如JESD204B的確定性延遲模式),在初始化階段配置鏈路參數(shù),通過(guò)多幀對(duì)齊序列(MFAS)實(shí)現(xiàn)數(shù)據(jù)幀邊界同步,降低通道間傳輸抖動(dòng)。

• 動(dòng)態(tài)負(fù)載均衡:當(dāng)某通道負(fù)載突變(如晶片尺寸差異),控制模塊實(shí)時(shí)調(diào)節(jié)各通道的PWM占空比和頻率,避免輸入電容瞬時(shí)過(guò)載,同時(shí)維持輸出電壓穩(wěn)定性。

三、技術(shù)挑戰(zhàn)與創(chuàng)新方向

1. 同步精度與功耗的平衡

多通道同步需高頻時(shí)鐘信號(hào)(如200kHz以上),但高頻率導(dǎo)致功耗和EMI增加。解決方案包括:

• 分頻器優(yōu)化:通過(guò)14位同步二進(jìn)制計(jì)數(shù)器將高頻晶振(如3.2MHz)分頻至工作頻率,降低單通道功耗;

• 隔離式傳輸:采用圖騰柱電路驅(qū)動(dòng)同步隔離變壓器,減少信號(hào)串?dāng)_。

2. 復(fù)雜工況下的魯棒性提升

• 狀態(tài)反饋閉環(huán):通過(guò)檢測(cè)模塊向靜電卡盤注入正弦波信號(hào),采集響應(yīng)信號(hào)并分析電容值變化,實(shí)時(shí)判斷晶片吸附狀態(tài)(未吸附/吸附/釋放),動(dòng)態(tài)調(diào)整高壓輸出;

• 容錯(cuò)機(jī)制:同步丟失時(shí)自動(dòng)觸發(fā)重同步協(xié)議,結(jié)合時(shí)間戳技術(shù)恢復(fù)時(shí)序。

四、應(yīng)用價(jià)值與展望

多通道同步高壓電源的應(yīng)用顯著提升了智能制造效能:

• 半導(dǎo)體制造:多晶圓并行處理產(chǎn)能提升30%,破片率下降至0.02%以下;

• 精密加工:通過(guò)靜電力動(dòng)態(tài)調(diào)控(毫秒級(jí)響應(yīng)),實(shí)現(xiàn)納米級(jí)定位精度。

未來(lái)技術(shù)將聚焦高密度集成(如GaN器件減小體積)與智能自適應(yīng)(AI預(yù)測(cè)負(fù)載變化),以滿足先進(jìn)制程對(duì)電源性能的極限需求。