靜電卡盤高壓電源諧振抑制技術:原理與創(chuàng)新方案

在半導體制造工藝中,靜電卡盤(Electrostatic Chuck, ESC)是晶圓蝕刻、沉積等關鍵工序的核心夾具,其穩(wěn)定性直接決定工藝精度。高壓電源作為靜電卡盤的能量來源,需提供±5kV以上的直流電壓以產(chǎn)生靜電力(約翰森-拉貝克效應),固定300mm晶圓。然而,高壓電源與卡盤電極、等離子體負載及濾波電路構成的復雜系統(tǒng)易引發(fā)諧振現(xiàn)象,導致電壓波動、晶圓位移甚至設備損毀。諧振抑制技術因此成為提升半導體良率的核心突破口。

諧振產(chǎn)生機制與影響

靜電卡盤系統(tǒng)的諧振主要由三類因素耦合引發(fā):

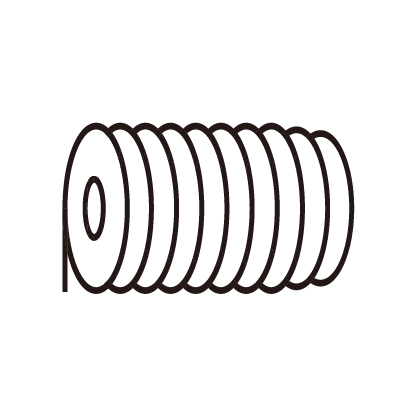

1. 電路參數(shù)非線性:高壓電源輸出的直流電壓需通過LCL濾波器消除高頻噪聲,但LCL拓撲中電感(L)與電容(C)的相互作用易在特定頻率下形成諧振點。例如,當電源載波頻率(通常為kHz級)與LCL的固有頻率重疊時,會激發(fā)電流振蕩,造成輸出電壓紋波增大。

2. 負載動態(tài)擾動:等離子體工藝中,反應腔內(nèi)的氣體電離狀態(tài)突變會導致負載阻抗在300%范圍內(nèi)波動,引發(fā)高壓電源的瞬時過載,進一步放大諧振幅值。

3. 多物理場耦合效應:靜電吸附過程產(chǎn)生的焦耳熱與晶圓-卡盤界面的接觸熱阻(波動幅度達20-30%)相互作用,形成熱-電反饋回路,加劇諧振頻率漂移。

此類諧振的直接影響包括:晶圓局部溫度漂移(>5℃)、吸附力不穩(wěn)(±3%偏差),最終導致刻蝕線寬均勻性惡化(CDU>0.8nm)。

諧振抑制的核心技術路徑

為應對上述挑戰(zhàn),業(yè)界從電路拓撲優(yōu)化、控制算法升級及材料創(chuàng)新三方面突破:

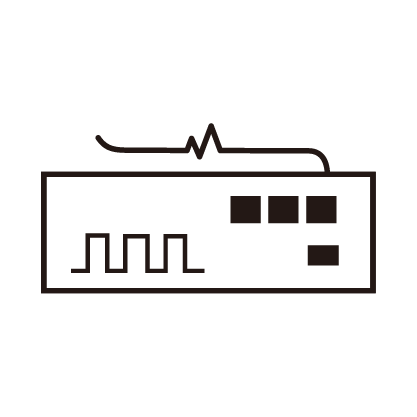

1. 高頻采樣與動態(tài)調(diào)制技術

• 多脈沖采樣控制:在單個三角載波周期內(nèi)進行N次等間隔電流/電壓采樣(N≥5),通過實時坐標變換(3s/2r)生成旋轉(zhuǎn)坐標系下的直軸分量(id/iq)。結(jié)合模型預測控制(MPC)算法,提前300ms預判諧振趨勢,動態(tài)調(diào)整PWM調(diào)制信號,將諧振能量抑制在毫秒級響應時間內(nèi)。

• 虛擬電阻阻尼:在數(shù)字控制環(huán)中植入虛擬阻抗模型,替代物理阻尼電阻,避免傳統(tǒng)無源阻尼的能耗問題。實驗表明,該方法可將LCL諧振峰衰減40dB以上,且系統(tǒng)效率提升5%。

2. 復合電極結(jié)構與場協(xié)同設計

• 蜂窩電極陣列:采用主-子電極分層設計,主電極(直徑200μm)負責靜電吸附,子電極(直徑50μm)嵌入熱敏材料執(zhí)行局部溫度補償。當檢測到諧振引發(fā)的熱點時,子電極自動調(diào)節(jié)局部電場強度,實現(xiàn)熱場均一性(±0.08℃)。

• 梯度介電層:表層覆蓋高導熱氮化鋁(κ=180W/mK)快速導離焦耳熱,底層采用高介電氮化硅(ε_r=7.5)阻斷電場穿透,從源頭上減少電場-熱場耦合擾動。

3. 量子傳感與智能反饋系統(tǒng)

• 納米級溫度監(jiān)測:集成金剛石氮空位(NV)色心傳感器,實現(xiàn)1μm空間分辨率與0.01℃/√Hz的溫敏精度,抗等離子體干擾能力較傳統(tǒng)RTD傳感器提升100倍。

• CNN熱場重構:基于卷積神經(jīng)網(wǎng)絡訓練熱分布圖像,動態(tài)映射晶圓表面溫度場,通過閉環(huán)控制補償95%以上的熱畸變,使刻蝕速率波動率降至±0.7%。

技術演進趨勢

未來諧振抑制技術將向多尺度融合方向發(fā)展:

• 仿生熱管理:模擬生物結(jié)構(如北極熊毛發(fā))開發(fā)各向異性導熱材料,實現(xiàn)軸向/徑向熱導率比>100。

• 光子-聲子調(diào)控:利用表面等離激元(SPP)定向傳輸熱能,結(jié)合聲子工程抑制晶格振動損耗,理論熱導率可提升10倍。

• 數(shù)字孿生平臺:構建高壓電源-靜電卡盤系統(tǒng)的多場耦合虛擬原型,通過實時仿真預判諧振風險,縮短工藝開發(fā)周期80%。

結(jié)語

諧振抑制技術是高壓電源在半導體高端裝備中應用的“安全閥”。通過電路-材料-算法的協(xié)同創(chuàng)新,新一代諧振抑制方案不僅解決了晶圓吸附穩(wěn)定性問題,更推動了刻蝕精度進入亞納米時代。隨著量子傳感與人工智能的深度嵌入,靜電卡盤系統(tǒng)將向零諧振、零熱擾動的終極目標邁進。