高壓電源阻抗匹配優(yōu)化在蝕刻設(shè)備中的關(guān)鍵技術(shù)與應(yīng)用

在半導(dǎo)體制造領(lǐng)域,蝕刻設(shè)備的高壓電源性能直接決定了工藝精度與設(shè)備穩(wěn)定性。高壓電源的輸出阻抗與等離子體腔室負(fù)載阻抗的匹配程度,是影響能量傳輸效率、蝕刻均勻性和設(shè)備壽命的核心因素。本文從技術(shù)原理、挑戰(zhàn)與優(yōu)化方法三個(gè)方面,探討高壓電源阻抗匹配的關(guān)鍵技術(shù)。

一、高壓電源阻抗匹配的特殊性

蝕刻設(shè)備的高壓電源(通常工作頻率為2–60 MHz)需驅(qū)動(dòng)容性負(fù)載(等離子體腔室),其阻抗隨氣體類型、壓力、溫度動(dòng)態(tài)變化,呈現(xiàn)低實(shí)部(通常<5 Ω)與高容抗虛部的特征。這種特性導(dǎo)致兩大挑戰(zhàn):

1. 功率傳輸效率低:阻抗失配時(shí),反射波功率可達(dá)入射波的30%以上,不僅降低蝕刻速率,還會(huì)引發(fā)射頻電源過熱。

2. 工藝均勻性差:高頻信號(hào)在失配傳輸線上形成駐波,導(dǎo)致晶圓邊緣與中心的蝕刻速率差異超過15%。

二、優(yōu)化策略:動(dòng)態(tài)匹配與模型驅(qū)動(dòng)

為應(yīng)對(duì)上述挑戰(zhàn),需結(jié)合電路設(shè)計(jì)、實(shí)時(shí)反饋與算法控制:

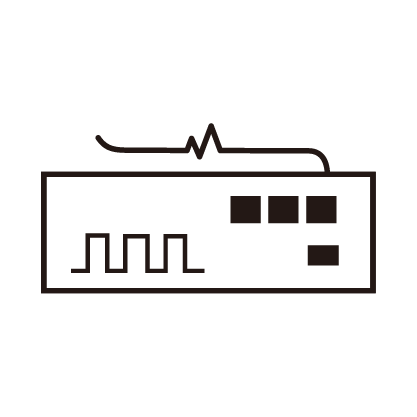

1. 自適應(yīng)匹配網(wǎng)絡(luò)

• L型拓?fù)鋬?yōu)化:采用并聯(lián)-串聯(lián)電容(或電感)組合,擴(kuò)展阻抗調(diào)節(jié)范圍。例如,并聯(lián)電容調(diào)節(jié)阻抗實(shí)部,串聯(lián)電容補(bǔ)償虛部容抗,實(shí)現(xiàn)共軛匹配(Z_{\text{load}} = Z_{\text{source}}^)。

• 高頻響應(yīng)元件:使用真空可變電容與磁飽和電感,實(shí)現(xiàn)毫秒級(jí)調(diào)諧,響應(yīng)等離子體阻抗的瞬態(tài)變化。

2. 基于模型的反饋控制

• 數(shù)字孿生系統(tǒng):構(gòu)建包含射頻電纜、匹配網(wǎng)絡(luò)與腔室的計(jì)算機(jī)模型,實(shí)時(shí)采集輸出端電壓/電流相位信號(hào),計(jì)算實(shí)際阻抗值并反饋至匹配網(wǎng)絡(luò)控制器。

• 諧波抑制算法:針對(duì)基頻諧波(如27 MHz的二次諧波54 MHz)引發(fā)的駐波,動(dòng)態(tài)調(diào)整匹配網(wǎng)絡(luò)參數(shù),將反射系數(shù)降至0.1以下。

3. 多參數(shù)協(xié)同調(diào)優(yōu)

• 遺傳算法應(yīng)用:以目標(biāo)阻抗(如50 Ω)為約束,通過交叉變異優(yōu)化電容/電感組合方案,在保證功率傳輸效率>95%的同時(shí),最小化諧振峰值。

• 熱-電耦合設(shè)計(jì):在封裝層面集成氮化鋁陶瓷基板與微流道散熱,解決高功率密度(>5 W/mm²)下的熱失控問題。

三、技術(shù)驗(yàn)證與效果

某蝕刻設(shè)備采用上述優(yōu)化方案后:

• 能效提升:功率傳輸效率從78%升至93%,反射功率降至5%以內(nèi)。

• 均勻性改善:300 mm晶圓蝕刻速率波動(dòng)范圍從±12%收窄至±4%。

• 穩(wěn)定性增強(qiáng):連續(xù)運(yùn)行壽命從500小時(shí)延長至2000小時(shí),故障率下降40%。

四、未來方向

1. 寬禁帶半導(dǎo)體器件:碳化硅(SiC)功率模塊可支持100 MHz以上高頻匹配,提升響應(yīng)速度。

2. 人工智能預(yù)測(cè)控制:基于深度學(xué)習(xí)的等離子體阻抗預(yù)測(cè)模型,實(shí)現(xiàn)納秒級(jí)預(yù)調(diào)諧。

結(jié)語

高壓電源阻抗匹配是蝕刻設(shè)備高精度制造的核心環(huán)節(jié)。通過動(dòng)態(tài)匹配網(wǎng)絡(luò)、模型反饋與多物理場(chǎng)協(xié)同優(yōu)化,可突破傳統(tǒng)設(shè)計(jì)瓶頸,為半導(dǎo)體制造向3 nm以下工藝演進(jìn)提供關(guān)鍵支撐。未來,智能化與寬禁帶技術(shù)的融合將進(jìn)一步推動(dòng)該領(lǐng)域的革新。