高壓電源驅(qū)動(dòng)薄膜沉積工藝提速

薄膜沉積是半導(dǎo)體制造中最基礎(chǔ)也是最耗時(shí)的工序之一,包括物理氣相沉積(PVD)、化學(xué)氣相沉積(CVD)和原子層沉積(ALD)等。在等離子體增強(qiáng)型沉積(PECVD, PEALD)中,高壓射頻(RF)或直流(DC)電源是產(chǎn)生和維持等離子體,驅(qū)動(dòng)沉積反應(yīng)的關(guān)鍵核心。高壓電源在這一環(huán)節(jié)的應(yīng)用性創(chuàng)新,主要集中在提高等離子體密度、均勻性、反應(yīng)速率,最終實(shí)現(xiàn)薄膜沉積工藝的提速和膜層質(zhì)量的優(yōu)化。

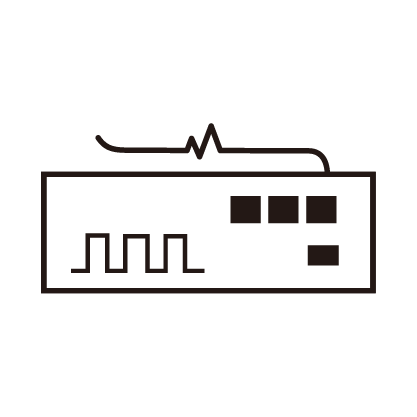

提速的核心在于高功率密度與脈沖化技術(shù)。傳統(tǒng)的連續(xù)波(CW)高壓射頻電源,在提升功率時(shí),容易導(dǎo)致等離子體中的電子溫度過(guò)高,引發(fā)不必要的副反應(yīng),甚至損傷襯底。而采用高壓脈沖等離子體技術(shù)(Pulsed Plasma),即通過(guò)高壓電源實(shí)現(xiàn)高頻率、高占空比(Duty Cycle)的脈沖輸出,可以在保持平均功率不變的情況下,極大提高等離子體峰值功率。峰值功率的提高可以瞬間產(chǎn)生更高密度的反應(yīng)自由基,從而顯著提高沉積速率。同時(shí),脈沖的“關(guān)斷”階段(Off-Time)為離子和自由基的弛豫、冷卻提供了時(shí)間,有效降低了襯底的損傷和薄膜的內(nèi)應(yīng)力。這要求高壓電源具備極快的上升/下降時(shí)間(納秒級(jí)甚至皮秒級(jí)),以及對(duì)脈沖波形(如方波、梯形波)的極高保真度。

其次,多頻/多模態(tài)匹配網(wǎng)絡(luò)與電源協(xié)同。為了優(yōu)化等離子體的特性,現(xiàn)代沉積設(shè)備往往需要同時(shí)注入多個(gè)頻率(如$13.56 \text{MHz}$, $2 \text{MHz}$, $400 \text{kHz}$)的高壓RF能量。低頻電源主要控制離子能量,影響轟擊效應(yīng)和致密性;高頻電源主要控制等離子體密度,影響沉積速率。高壓電源的創(chuàng)新在于其多通道、同步可調(diào)的設(shè)計(jì),能實(shí)時(shí)調(diào)整不同頻率電源的相位、功率和阻抗匹配。采用先進(jìn)的L-C-C或$\pi$型自動(dòng)匹配網(wǎng)絡(luò),配合高速數(shù)字控制,可以確保在高功率脈沖輸出時(shí),電源與等離子體負(fù)載(等離子體阻抗在脈沖開(kāi)啟和關(guān)閉瞬間會(huì)劇烈變化)之間的阻抗始終保持在$50 \Omega$左右,將反射功率降至最低,最大化有效功率傳輸,實(shí)現(xiàn)等離子體的快速建立和穩(wěn)定維持。

再者,直流偏置與等離子體勢(shì)能控制的應(yīng)用。在某些沉積工藝中(如PVD),需要對(duì)襯底施加高壓直流(DC)偏置電壓,以控制正離子轟擊襯底的能量。高壓電源必須提供一個(gè)極低噪聲、極高穩(wěn)定性的直流輸出,以確保離子能量的精確控制。創(chuàng)新的高壓DC電源結(jié)合了快速電弧抑制技術(shù),在等離子體放電過(guò)程中,電極或腔體內(nèi)可能因顆粒或局域不均勻性產(chǎn)生電弧。高壓電源必須在微秒甚至納秒級(jí)別內(nèi)檢測(cè)到電弧的發(fā)生,并迅速關(guān)斷或轉(zhuǎn)移能量,避免對(duì)電源和設(shè)備造成損害,確保工藝的連續(xù)性。這種快速響應(yīng)能力是實(shí)現(xiàn)沉積工藝提速和高良率的關(guān)鍵保障。

最后,電源與工藝過(guò)程的深度集成。傳統(tǒng)的電源僅作為能量輸出單元,而現(xiàn)代高壓電源則集成了等離子體診斷功能。通過(guò)測(cè)量電源的輸出電壓、電流波形,結(jié)合腔體內(nèi)部的傳感器數(shù)據(jù)(如光學(xué)發(fā)射光譜OES),高壓電源可以作為實(shí)時(shí)等離子體狀態(tài)的感知器。這種深度集成允許控制系統(tǒng)通過(guò)算法實(shí)時(shí)調(diào)整高壓電源的參數(shù)(如脈沖頻率、占空比、多頻功率比),以補(bǔ)償工藝漂移,維持最佳的反應(yīng)速率和薄膜質(zhì)量。例如,在薄膜厚度即將達(dá)到目標(biāo)時(shí),電源可以平滑地降低功率,實(shí)現(xiàn)沉積速率的“軟著陸”,確保薄膜厚度的超高精度控制。