高壓電源與半導體測試的精密對接

在半導體產(chǎn)業(yè)蓬勃發(fā)展的當下,半導體測試作為保障芯片質(zhì)量與性能的關(guān)鍵環(huán)節(jié),對測試設(shè)備的精度與穩(wěn)定性提出了嚴苛要求。高壓電源,作為半導體測試系統(tǒng)中不可或缺的一部分,肩負著為各類測試提供精準高電壓激勵的重任,其與半導體測試的精密對接,直接關(guān)系到整個半導體制造流程的成敗。

半導體測試涵蓋了從芯片制造初期的晶圓測試,到封裝完成后的成品測試等多個階段。在晶圓測試階段,微小的芯片結(jié)構(gòu)需要在高電壓下進行電學特性檢測,以篩選出潛在的缺陷產(chǎn)品。高壓電源在此必須能夠輸出穩(wěn)定、精確且可精細調(diào)控的電壓。例如,對于先進制程下的晶體管擊穿電壓測試,電壓精度需控制在極小的誤差范圍內(nèi),稍有偏差就可能導致誤判,使良品被誤淘汰或不良品流入下一工序,給企業(yè)帶來巨大損失。

從技術(shù)原理上講,高壓電源要實現(xiàn)精密對接,首先需具備出色的電壓調(diào)節(jié)能力。采用先進的數(shù)字化控制技術(shù),能夠依據(jù)測試程序設(shè)定,快速、平滑地調(diào)整輸出電壓,從幾伏到數(shù)千伏的寬量程切換中,保持電壓的線性度與穩(wěn)定性。同時,為應對半導體測試中的動態(tài)負載變化,高壓電源應擁有快速的響應特性,確保在負載突變時,電壓瞬間恢復穩(wěn)定,避免測試信號的抖動干擾測試結(jié)果。

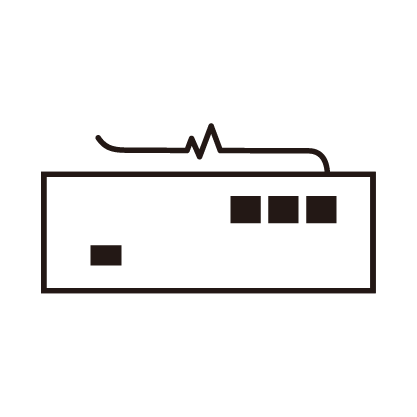

在實際對接過程中,與測試設(shè)備的兼容性至關(guān)重要。高壓電源需適配不同半導體測試系統(tǒng)的接口標準,無論是基于傳統(tǒng) GPIB 通信協(xié)議,還是新興的高速以太網(wǎng)接口,都要確保數(shù)據(jù)傳輸?shù)膶崟r性與準確性,以便測試系統(tǒng)精準控制電源輸出。而且,電源的輸出噪聲必須被嚴格抑制,半導體測試中的微弱電信號極易受噪聲干擾,毫伏級甚至微伏級的噪聲都可能掩蓋芯片真實的電學特性,使測試數(shù)據(jù)失效。

為保證長期穩(wěn)定運行,高壓電源的可靠性設(shè)計不可或缺。采用冗余電路結(jié)構(gòu),在部分元件出現(xiàn)故障時,仍能維持基本功能,避免測試中斷。散熱管理同樣關(guān)鍵,高功率運行下,高效的散熱系統(tǒng)能防止因溫度漂移引發(fā)的電壓波動,確保電源在恒溫環(huán)境下輸出精準電壓,滿足半導體測試長時間、高強度的工作需求。

高壓電源與半導體測試的精密對接是一項系統(tǒng)工程,涉及電子技術(shù)、材料科學、熱管理等多領(lǐng)域協(xié)同創(chuàng)新。只有持續(xù)攻克技術(shù)難題,優(yōu)化對接細節(jié),才能為半導體產(chǎn)業(yè)源源不斷輸送高質(zhì)量芯片提供堅實保障,推動整個半導體行業(yè)邁向更高的精度與效率巔峰,在全球科技競爭浪潮中穩(wěn)健前行。