光刻機(jī)高壓電源多諧振腔協(xié)同穩(wěn)壓技術(shù)及應(yīng)用

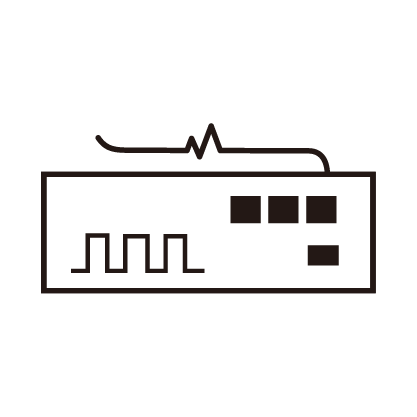

在先進(jìn)半導(dǎo)體制造中,光刻機(jī)作為 “芯片印鈔機(jī)”,其曝光精度直接決定芯片制程極限,而高壓電源作為光刻光源(如極紫外光 EUV)的能量核心,需滿足納米級(jí)制程對(duì)電壓穩(wěn)定性(紋波率≤0.1%)、動(dòng)態(tài)響應(yīng)速度(μs 級(jí))的嚴(yán)苛要求。傳統(tǒng)單諧振腔高壓電源因諧振頻率單一,難以同時(shí)抑制寬頻段紋波與快速響應(yīng)負(fù)載波動(dòng) —— 當(dāng)光刻機(jī)晶圓臺(tái)進(jìn)行納米級(jí)步進(jìn)運(yùn)動(dòng)時(shí),光源負(fù)載會(huì)出現(xiàn)瞬時(shí)脈沖變化,單諧振腔電源易產(chǎn)生電壓過(guò)沖或跌落,導(dǎo)致曝光能量不均,影響圖形轉(zhuǎn)移精度。

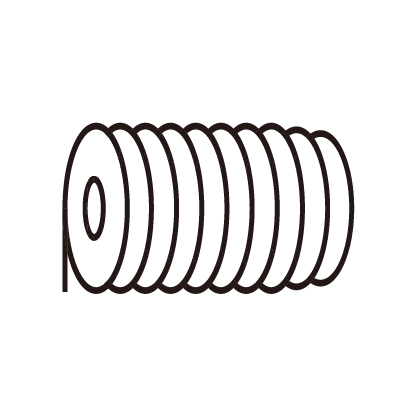

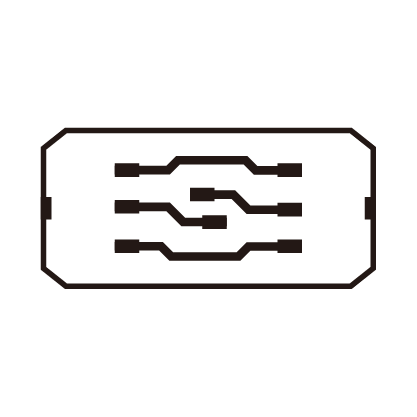

多諧振腔協(xié)同穩(wěn)壓技術(shù)通過(guò)拓?fù)浣Y(jié)構(gòu)創(chuàng)新與控制策略?xún)?yōu)化,解決了這一矛盾。該技術(shù)采用 “串聯(lián) - 并聯(lián)混合諧振腔拓?fù)?rdquo;,將 3-5 個(gè)獨(dú)立諧振腔按頻率分段設(shè)計(jì):低頻頻段(50-100kHz)諧振腔負(fù)責(zé)抑制電網(wǎng)引入的基波紋波,中頻頻段(500kHz-1MHz)諧振腔針對(duì)電源開(kāi)關(guān)噪聲,高頻頻段(5-10MHz)諧振腔則應(yīng)對(duì)負(fù)載瞬時(shí)波動(dòng)。各諧振腔通過(guò) FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列)控制單元實(shí)現(xiàn)協(xié)同通信,實(shí)時(shí)采集輸出電壓波形與負(fù)載電流變化,采用 “加權(quán)自適應(yīng)算法” 動(dòng)態(tài)分配各腔的穩(wěn)壓權(quán)重 —— 當(dāng)負(fù)載出現(xiàn) μs 級(jí)脈沖時(shí),高頻諧振腔優(yōu)先啟動(dòng)電容放電補(bǔ)償,同時(shí)中低頻諧振腔同步調(diào)整儲(chǔ)能狀態(tài),避免單一腔室過(guò)載。

在實(shí)際應(yīng)用中,該技術(shù)已在 14nm 及以下先進(jìn)制程光刻機(jī)中驗(yàn)證:其輸出電壓紋波率可降至 0.05% 以下,動(dòng)態(tài)響應(yīng)時(shí)間縮短至 2μs,較傳統(tǒng)電源使光刻圖形線寬誤差減少 30%,良率提升 8%-12%。此外,協(xié)同機(jī)制還降低了單個(gè)諧振腔的功率損耗,電源整體效率從 85% 提升至 92%,契合半導(dǎo)體制造的低能耗需求。未來(lái)隨著 3nm、2nm 制程發(fā)展,多諧振腔技術(shù)將進(jìn)一步融合 AI 預(yù)測(cè)控制,通過(guò)學(xué)習(xí)不同晶圓曝光場(chǎng)景的負(fù)載規(guī)律,實(shí)現(xiàn) “預(yù)判式穩(wěn)壓”,為極紫外光刻提供更穩(wěn)定的能量支撐。